# JVC

# SERVICE MANUAL

**DVD PLAYER**

## XV-521BK/523GD/522SL

##

| Area Suffix<br>XV-523GD/522SL                               |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------|--|--|--|--|--|--|--|--|

| B U.K.                                                      |  |  |  |  |  |  |  |  |

| EN ····· Northern Europe                                    |  |  |  |  |  |  |  |  |

| EG ··· Germany, France, Greece,<br>Netherlands, Switzerland |  |  |  |  |  |  |  |  |

| ES Spain, Italy                                             |  |  |  |  |  |  |  |  |

### **Contents**

| Safety precautions 1-2       | Main Adjustment1-14          |

|------------------------------|------------------------------|

| Importance administering     | Troubleshooting1-21          |

| point on the safety 1-3      | Precautions for service 1-22 |

| Disassembly method ····· 1-4 | Description of major ICs1-23 |

## Safety precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (△) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

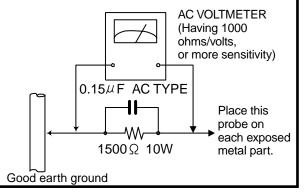

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

- ◆ Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500Ω 10W resistor paralleled by

a 0.15  $\mu {\rm F}$  AC-type capacitor between an exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. voltage measured Any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

## Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

AUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

## Dismantling and assembling the traverse unit

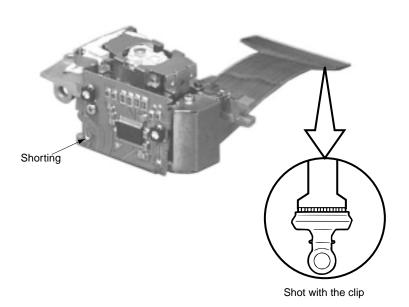

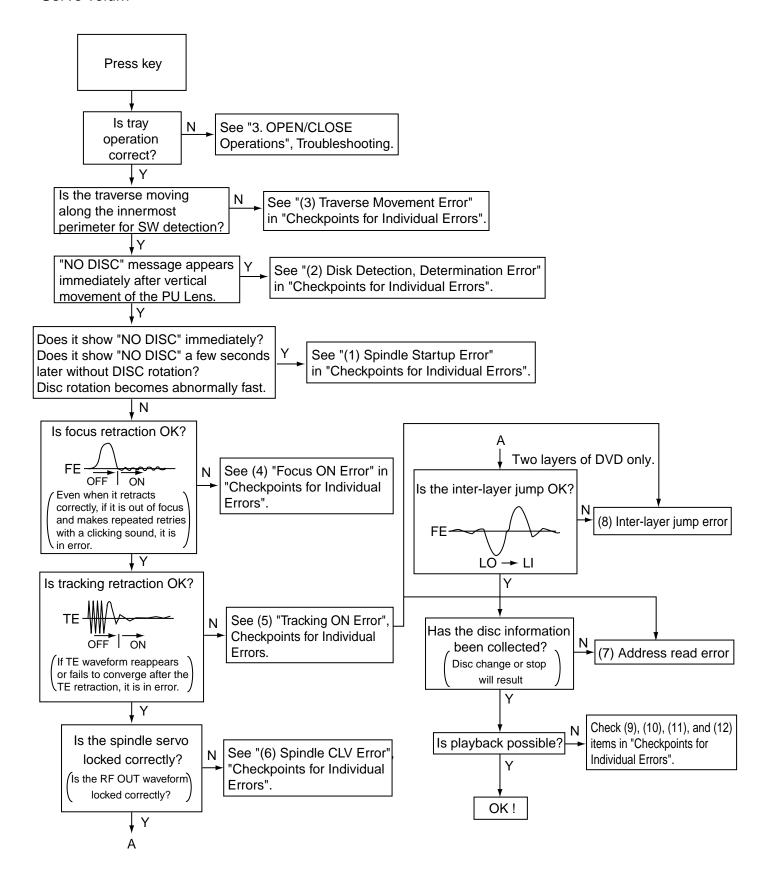

## 1. Notice regarding replacement of optical pickup

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs to the optical pickup or connected devices.

(Refer to the section regarding anti-static measures.)

- 1. Do not touch the area around the laser diode and actuator.

- 2. Do not check the laser diode using a tester, as the diode may easily be destroyed.

- 3. It is recommended that you use a grounded soldering iron when shorting or removing the laser diode. Recommended soldering iron: HAKKO ESD-compatible product

- 4. Solder the land on the optical pickup's flexible cable.

- Note: Short the land after shorting the terminal on the flexible cable using a clip, etc., when using an ungrounded soldering iron.

- Note: After shorting the laser diode according to the procedure above, remove the solder according to the text explanation.

## **Disassembly method**

### < Main body>

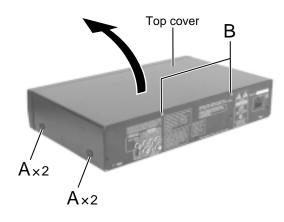

#### ■Removing the top cover (See Fig.1)

- 1. Remove the four screws A on both side of the body.

- 2. Remove the two screws B on the back of the body.

- 3. Lift up the rear part of the top cover while pulling the lower part of the sides, then detach upward.

Fig.1

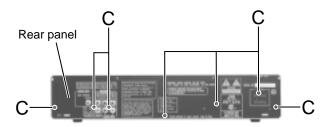

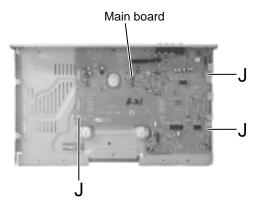

#### ■ Removing the rear panel (See Fig.2)

- Prior to performing the following procedure, remove the top cover.

- 1. Remove the seven screws C on the back of the body.

Fig.2

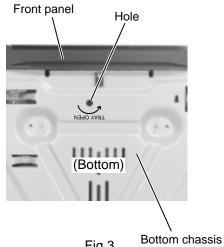

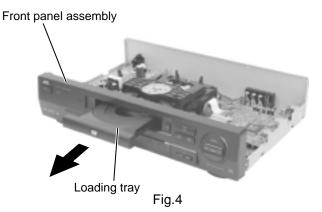

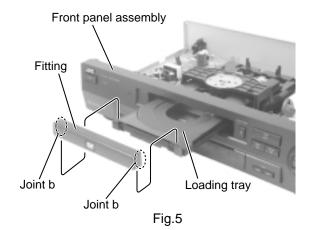

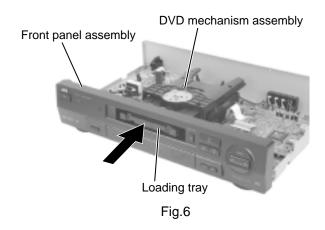

#### ■ Removing the fitting (See Fig.3 to 6)

· Prior to performing the following procedure, remove the top cover.

ATTENTION: To remove the front panel assembly and the DVD mechanism assembly, remove the fitting in advance.

- by hand —

- 1. Turn over the body. Insert a screwdriver into the hole of the bottom chassis and turnit. The loading tray will be ejected out of the front panel assembly.

- 2. Pull the loading tray toward the front.

- 3. Remove the fitting upward from the loading tray at the joints b.

- 4. Push and return the loading tray.

Fig.3

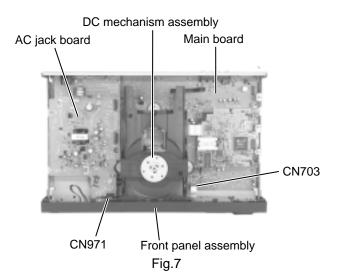

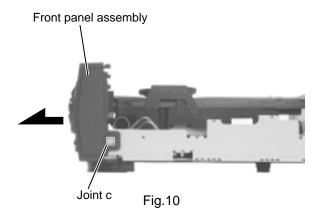

## ■ Removing the front panel assembly (See Fig.7 to 10)

- Prior to performing the following procedure, remove the top cover and the fitting.

- 1. Disconnect the card wire from connector CN703 on the main board.

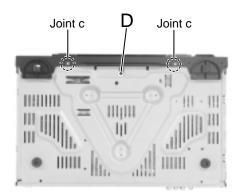

- 2. Turn over the body and remove the screw D attaching the front panel assembly.

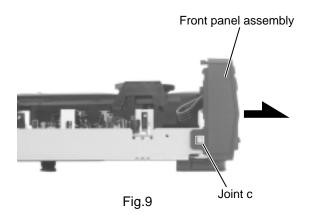

- 3. Release the five joints c on both sides and bottom of the body and remove the front panel assembly toward the front.

ATTENTION: The connector CN832 on the front panel assembly and CN971 on the AC jack board will be disconnected at the same time.

Fig.8

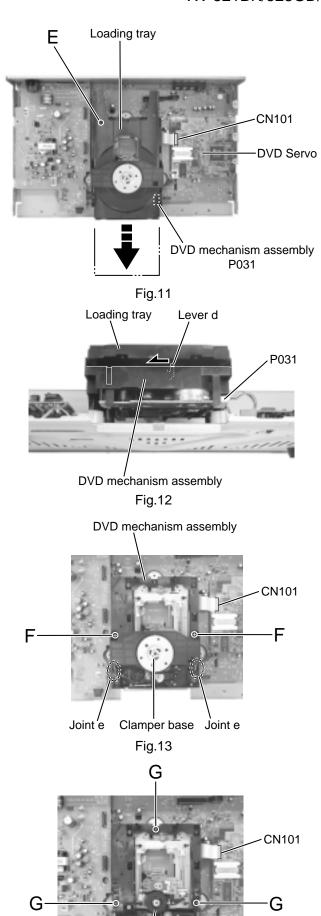

## ■ Removing the DVD mechanism assembly (See Fig.11 to 14)

- Prior to performing the following procedure, remove the top cover and the front panel assembly.

- Disconnect the card wire from connector CN101 on the DVD Servo.

- 2. Disconnect the harness from connector CN031 on the DVD mechanism assembly.

- 3. Remove the screw E on the rear left part of the loading tray.

- 3. From the front side of the DVD mechanism assembly, move the lever d in the direction of the arrow and pull out the loading tray.

- 4. Remove the two screws F on the upper side of the DVD mechanism assembly. Then release the two joints e and detach the clamper base back-upward.

- 5. Remove the three screws G attaching the DVD mechanism assembly.

DVD mechanism assembly Fig.14

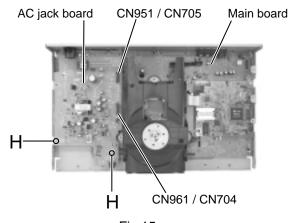

## ■ Removing the AC jack board (See Fig.15 and 16)

- Prior to performing the following procedure, remove the top cover and the front panel assembly.

- Remove the two screws H attaching the AC jack board.

- 2. Remove the two screws C on the rear panel.

- Disconnect connector CN951 and CN961 on the AC jack board from CN704 and CN705 on the main board respectively.

Fig.15

Fig.16

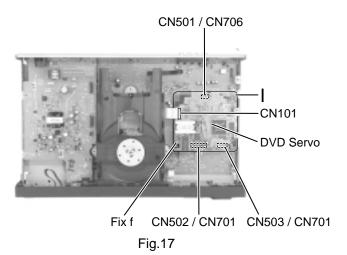

## ■Removing the DVD Servo (See Fig.17 and 18)

- Prior to performing the following procedure, remove the top cover.

- 1. Remove the screw I attaching the DVD Servo.

- 2. Pull out the DVD Servo from the fix f while pinching the fix f.

- 3. Disconnect connector CN501, CN502 and CN503 on the DVD Servo from CN601, CN701 and CN706 on the main board respectively.

Fix f

DVD Servo

Main board

Fig.18

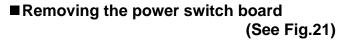

## ■Removing the main board (See Fig.19 and 20)

- Prior to performing the following procedure, remove the top cover, the front panel assembly, the DVD mechanism assembly, the AC jack board and the DVD Servo.

- 1. Remove the three screws J attaching the main board.

- 2. Remove the two screws C on the rear panel.

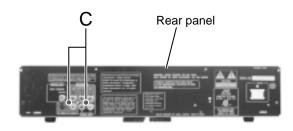

• Prior to performing the following procedure, remove the top cover and the front panel assembly.

- 1. Unsolder connector FW841 on the power switch board on the back of the front panel assembly.

- 2. Remove the two screws K attaching the power switch board.

- 3. Push the two tabs g in the direction of the arrow and remove the power switch board.

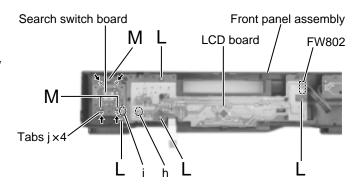

## ■ Removing the LCD board (See Fig.22)

- Unsolder connector FW802 and soldering h on the LCD board.

- 2. Remove the four screws L attaching the LCD board.

## ■Removing the search switch board (See Fig.20)

- 1. Unsolder soldering i on the search switch board.

- 2. Remove the three screws M.

- 3. Release the four tabs j in the direction of the arrow and remove the search switch board.

Fig.19

Fig.20

Fig.22

#### <DVD mechanism>

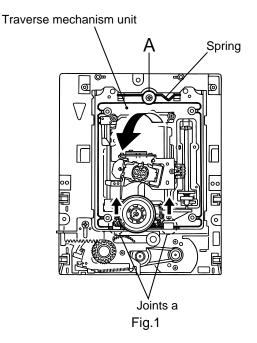

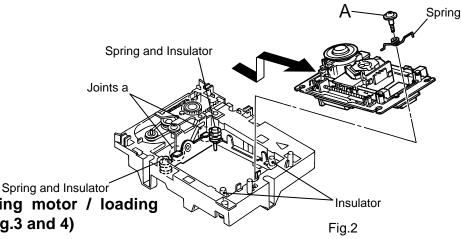

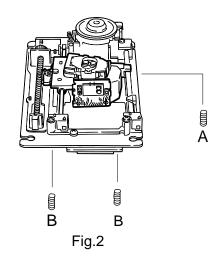

## ■ Removing the traverse mechanism unit (See Fig.1 and 2)

- 1. Remove the screw A and the spring on the upper side of the loading base assembly.

- 2. Move the rear part of the traverse mechanism unit upward and pull backward to release the two joints a with the base chassis.

ATTENTION: When reattaching, engage the two joints a and make sure the front springs and the four insulators of the traverse mechanism unit are correctly attached.

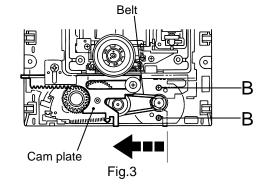

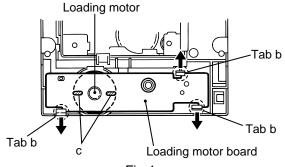

■Removing the loading motor / loading motor board (See Fig.3 and 4)

- 1. Move the cam plate on the upper side of the loading base assembly in the direction of the arrow.

- 2. Remove the belt from the motor pulley.

- 3. Remove the two screws B attaching the loading motor.

- 4. Turn over the loading base assembly and release the loading motor board from the three tabs b while spreading them outward. The loading motor board will be detached with the loading motor.

- 5. Unsolder soldering c on the loading motor board and remove the loading motor.

Ref.: To remove the loading motor board only, unsolder soldering c on the loading motor and release the three tabs b.

Fig.4

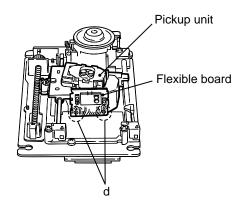

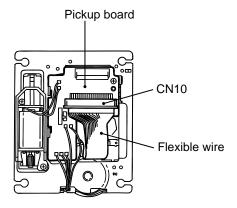

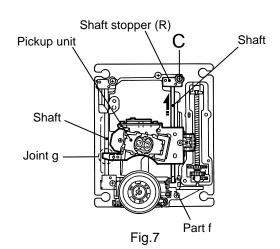

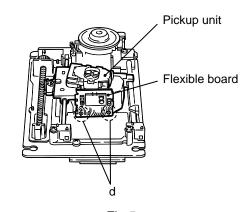

#### ■Removing the pickup (See Fig.5 to 9)

- It is not necessary to remove the traverse mechanism unit.

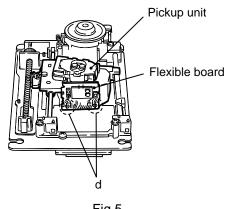

- 1. Solder soldering d on the flexible board next to the pickup unit.

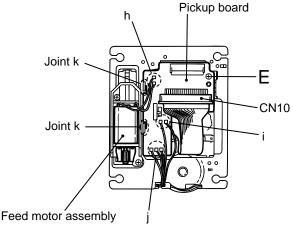

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN10 on the pickup board.

- ATTENTION: Disconnecting the flexible wire without soldering may cause damage to the pickup.

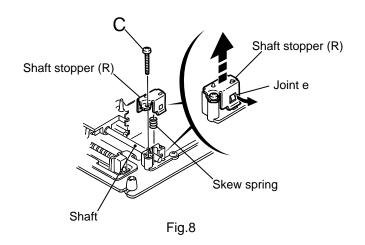

- 3. Remove the screw C attaching the shaft stopper (R) on the upper side of the traverse mechanism unit. Pull the side of the shaft stopper (R) outward to release the joint e and remove it upward. Remove the skew spring at the same time.

- 4. Move the shaft in the direction of the arrow to release it from the part f.

- 5. Release the joint g with the shaft and remove the pickup with the shaft.

- 6. Pull out the shaft.

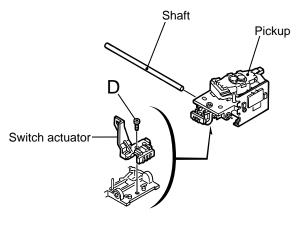

- 7. Remove the screw D attaching the switch actuator.

Fig.5

Fig.6

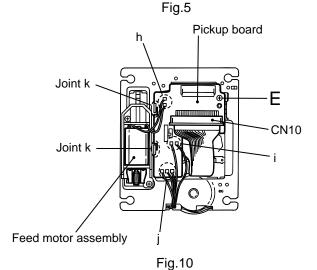

### ■Removing the pickup board (See Fig.5 and 10)

- It is not necessary to remove the traverse mechanism unit.

- 1. Solder soldering d on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit. disconnect the flexible wire from CN10 on the pickup board.

- ATTENTION: Disconnecting the flexible wire without soldering may cause damage to the pickup.

- 3. Unsolder soldering h, i and j of each harness on the pickup board.

- 4. Remove the screw E attaching the pickup board and release the two joints k.

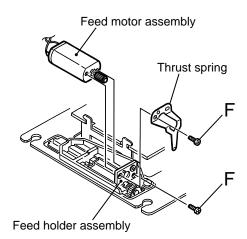

### ■Removing the feed motor assembly (See Fig.5, 10 and 11)

- · Prior to performing the following procedure, remove the traverse mechanism unit.

- 1. Solder soldering d on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN10 on the pickup board.

- ATTENTION: Disconnecting the flexible wire without soldering may cause damage to the pickup.

- 3. Unsolder soldering h of the motor harness on the pickup board.

- 4. Remove the two screws F attaching the feed motor assembly and remove the thrust spring. Move the feed motor assembly in the direction of the arrow to pull it out from the feed holder.

Fig.5

Fig.10

Fig.11

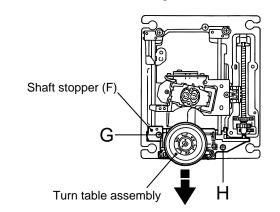

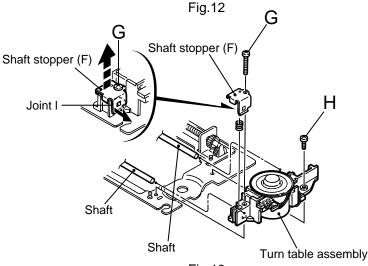

## ■ Removing the turn table assembly (See Fig.5, 10, 12 and 13)

- Prior to performing the following procedure, remove the traverse mechanism unit.

- 1. Solder soldering d on the flexible board next to the pickup unit.

- From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN10 on the pickup board.

- ATTENTION: Disconnecting the flexible wire without soldering may cause damage to the pickup.

- 3. Unsolder soldering i and j of the harness extending from the turning table assembly to the pickup board.

- 4. Remove the screw G attaching the shaft stopper (F) on the upper side of the traverse mechanism unit. Pull the side of the shaft stopper (F) outward to release the joint I and remove it upward. Remove the spring at the same time.

- 5. Remove the screw H attaching the turn table assembly.

- 6. Move the turn table assembly outward and pull out from the shaft. Then remove it from the base chassis.

## Main adjustment

Adjustment and confirmation matter

(1) Auto adjustment method

If microprocessor (IC401, IC402, IC791, IC403) or Pick-up is replaced, initialize the DVD player in the following matter:

- 1. Initialize the DVD player in the following matter:

- 1) Make sure that no disc is on the tray.

- 2)Insert the power pulag to the outret while pressing "PLAY" and "OPEN/CLOSE" button at the same time.

- FL Display indicate "TEST \* \* \(\frac{1}{2}\)" ( \* \*; Version. \(\frac{1}{2}\); Region code)

- 3) Press 3D-PHONIC button. And EEPROM initialize start.

- 4) When indicate "V.REPLACE" on the display, initialize finished.

- \* The test mode is cancelled when the power is turned off.

#### (2) Flap adjustment of the Pick-up guide shaft

- 1) Make sure that no disc is on the tray.

- 2)Insert the power pulag to the outret while pressing "PLAY" and "OPEN/CLOSE" button at the same time.

FL Display indicate "TEST \* \* \(\pm\)" ( \* \*; Version. \(\pm\); Region code)

3)Press the "OPEN/CLOSE" button to move the tray outward.

Put the Test Disc (VT-501)on the tray and press "OPEN/CLOSE" button.

The tray should move inward (Note:Don't push to close the tray directly by hand etc.

- 4)Press the "PLAY" button.

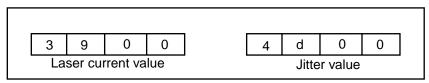

- 5)The laser current and the jitter value is displayed on the FL indicator as follows.

FL indicator

- 6)Set the Jitter value of FL indicator to minimum by adjusting the pick-up guide shaft flap.

- \* The test mode is cancelled when the power is turned off.

#### Flap adjustment method

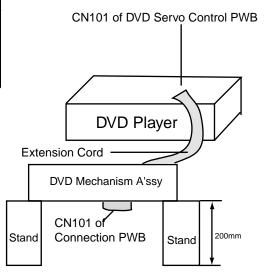

| Measurement                            | Adjustment point |                     |  | Mode                | Disc    |  |  |

|----------------------------------------|------------------|---------------------|--|---------------------|---------|--|--|

| FL Display                             | Refer to Fig.2   |                     |  | Reproduction<br>art | VT-501  |  |  |

| Measurement machin                     | ne connections   |                     |  | Extension cord No.  |         |  |  |

| No need                                |                  | Refer to Fig.1 QUQ6 |  |                     | -4040AJ |  |  |

| General tool : Hex-head wrench(1.27mm) |                  |                     |  |                     |         |  |  |

"Flap adjustment" of the Pick-up guide shaft adjusts "Tangential adjustment machine screw" A and "Tilt adjustment machine screw" B from the DVD Mechanism A'ssy bottom.

- 1. The part at the center on the DVD test disc is reproduced.

- 2. The flap adjustment screws is turned alternately and set the jitter value of FL indicator to its minimum.

#### Note

- 1. The tangential adjustment is done finish and, then, tilt is adjusted.

- 2.The repeat the adjustment 2-3 times, for best result.

- 3. The final adjustment should be tilt adjustment.

#### Confirmation after adjustment.

Confirm to reproduce video CD and CD after the DVD test disc is adjusted and to find abnormality.

Fig.1

#### (3) About keeping the disc

As for the DVD test disc, plane accuracy is demanded. Please note the keeping place on the disc.

- 1. Please do not put the disc directly on the work desk etc. after uses .

- 2.To keep the planarity of the disc, politely handle ,and please put in a special case and keep the disc vertically after uses .

- Please keep keeping the disc in a cool place where direct sunshine and the air-conditioning wind do not drive.

- 3. When the disc curves, an accurate adjustment cannot be done. Please exchange for a new test disc and adjust optics.

- 4 Other discs might not be able to be reproduced when adjusting on a curved disc.

#### Point of adjustment

- \* Please execute the static electricity protection measures before starting the adjustment.

- \* When the following parts are exchanged,optical adjustment "Adjust the flap of Pick-up guide shaft" is necessary.

- 1. The disc motor was exchanged.

- 2. The laser pick up was exchanged.

- 3. The traverse motor unit was exchanged.

#### Note

Additionally, please adjust the flap of the disc motor when the picture quality deterioration is seen .The basic adjustment though, is unnecessary for part exchange in the traverse. An optical adjustment in the laser pick up cannot be done.

Please adjust the flap of the disc motor after exchanging the laser pick up.

\* When the traverse unit is exchanged, the adjustment is basically unnecessary.

## **Checkpoints for individual errors**

#### (1) Spindle startup error

- 1. Defective spindle motor

- \* Is the resistance between CN101 "34-35" and "36-37" about 10 to 6 ohms? (Measure it with the power OFF.)

- \* Is the voltage waveform for the hall element CN101"40" square-wave? (During rotation)

- 2. Defective spindle driver (IC271)

- \* Is DC voltage applied to IC271"14-15"?

- \* Is IC271"25" set to "H" (SPMUTE)?

- 3. Servo IC

Is control available at the motor driver?

- \* IC201"52" → R290 50% duty during stop. Variable during rotation (Fluctuates especially during startup.) If no control available: pattern servo IC, IC201.

- 4. Is FG input in the servo IC?

- \* IC271"42"  $\rightarrow$  IC271"41"  $\rightarrow$  0275  $\rightarrow$  IC201"53" (FG) FG waveform observation If no FG input: pattern IC271, IC201.

#### (2) Disk detection, distinction error (no discs, no REFNV)

- 1. Defective laser

- 2. Defective front-end processor (IC101)

- 3. Defective APC circuit → Q101, Q102

- 4. Defective pattern

A pattern between all CN101 PIC related patterns and the IC101

- 5. Defective servo IC (IC201)

- 6. IC101

Are IC101"20"(AS), IC101"41"(RFENV), and IC101"22"(FE) included in the signal to IC201?

#### (3) Traverse movement error

- 1. Defective traverse motor

- \* Is voltage applied between CN101 "38" and "39"?

- 2. Defective BTL driver

- \* Is voltage applied on IC271 "9" and "10"?

- \* Is MUTE1 terminal "26" of IC271 set to "H"?

- \* Is drive voltage applied to servo IC201"51"? Defective servo IC or defective pattern

#### (4) Focus ON error

- 1. Is FE produced? → Pattern, IC101

- 2. Is FODRV signal produced? (R280) → Pattern, IC201

- 3. Is drive voltage available?

If not available: pattern, driver, or mechanism. (Turn the power OFF then measure the resistance between CN101 "30" and "31".)

- 4. Defective mechanism

#### (5) Tracking ON error

- 1. When tracking loop is not retracted, TE waveform does not converge.

- 2. Defective mechanism

The possible cause for unavailability of correct retraction is that automatic adjustment cannot be made successfully.

- 3. Driver and its related parts (IC271)

- Constant and IC defects (When it was passed during the adjustment below without going into an abnormal condition)

- 4. Servo IC (IC201)

When automatic adjustment was unsuccessful due to defective ICs.

#### (6) Spindle CLV error

- 1. When the spindle servo is not locked successfully, RF eye-pattern cannot be locked successfully.

- 2. IC101"35" (RF OUT), IC101"30" (RF-), IC101"31"(RF+)

- 3. Is the driver spindle signal input not clipped by the output signal?

- 4. Is the transistor ON?

- 5. Defective spindle motor or driver.

- 6. Other errors may be caused by defective mechanism (jitter) etc. in IC 101 and IC201.

#### (7) Address Read Failure

The failure may be caused by many possible factors and it is difficult to pick one out. However, the following are among the possible causes.

- 1. Defective mechanism (significant jitter)

- 2. IC (IC201, IC301, IC401)

- 3. Contaminated or damaged discs.

#### (8) Inter-layer Jump error

- 1. Defective mechanism.

- 2. Defective constant or IC of the Driver IC (IC271).

- 3. Defective servo IC (IC201).

#### [During Normal Playback of DVD]

#### (9) No image or sound

- 1. Search is not possible.

- a) Can the transistor be switched ON?If not, see "(5) Tracking ON Error" in "Checkpoints for Individual Errors".

- b) Is the feed operation normal?

In case of an error, check "(3) Traverse Movement Error" in "Checkpoints for Individual Errors" or check if there is any point where the feed mechanism is caught.

- (10) Picture disturbance or unusual sound once every few seconds.

Check if the feed operation during playback is smooth.

If not, perhaps the mechanism is caught.

#### (11) Others (Example of special cases that occurred in the past)

- 1. Occasionally, the picture becomes a block or stops.

- The condition along the innermost perimeter is OK.

However, at the outermost corner, the picture becomes

a block or stops frequently.

Inaccurate tilting may also be the cause.

So, perform readjustment of mechanism tilting.

With these symptoms, it is probably a bad jitter value that is causing the problem.

#### [During normal CD playback]

(12) Is TOC read possible? NO Refer to the Servo flow.

CD-DA shows the total time. V-CD changes to double-speed.

- The OSD screen shows "NO READING" message.

(9) As in the case of "Search is not possible", check the feed and tracking.

- 2. Time display is available, but there is no sound. Check DAC, etc. except the Servo.

- 3. Time flow unstable. Picture abnormal (V-CD). Measure the jitter.

- 4. Check whether the discs is contaminated or damaged.

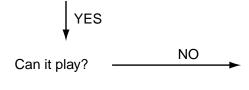

## **Troubleshooting**

#### Servo volum

## **Precautions for service**

### Handling of Traverse Unit and Laser Pickup

- 1. Do not touch any peripheral element of the pickup or the actuator.

- 2. The traverse unit and the pickup are precision devices and therefore must not be subjected to strong shock.

- 3. Do not use a tester to examine the laser diode. (The diode can easily be destroyed by the internal power supply of the tester.)

- 4. To replace the traverse unit, pull out the metal short pin for protection from charging.

- 5. When replacing the pickup, after mounting a new pickup, remove the solder on the short land which is provided at the center of the flexible wire to open the circuit.

- 6. Half-fixed resistors for laser power adjustment are adjusted in pairs at shipment to match the characteristics of the optical block.

- Do not change the setting of these half-fixed resistors for laser power adjustment.

#### Destruction of Traverse Unit and Laser Pickup by Static Electricity

Laser diodes are easily destroyed by static electricity charged on clothing or the human body. Before repairing peripheral elements of the traverse unit or pickup, be sure to take the following electrostatic protection:

- 1. Wear an antistatic wrist wrap.

- 2. With a conductive sheet or a steel plate on the workbench on which the traverse unit or the pick up is to be repaired, ground the sheet or the plate.

- 3. After removing the flexible wire from the connector (CN101), short-circuit the flexible wire by the metal clip.

- 4. Short-circuit the laser diode by soldering the land which is provided at the center of the flexible wire for the pickup. After completing the repair, remove the solder to open the circuit.

When replacing the Mechanism Unit, turn ON the laser switch that is located at the lower of the pick up after replacement.

## **Description of major ICs**

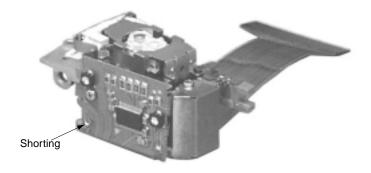

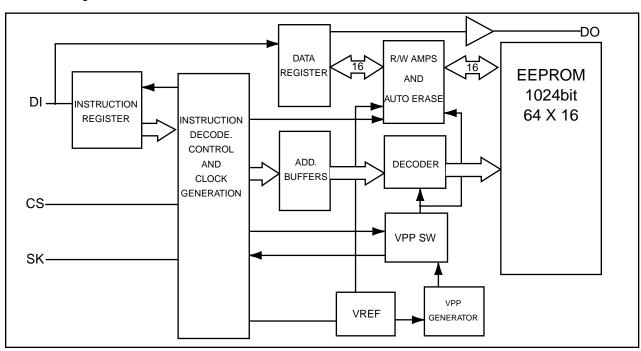

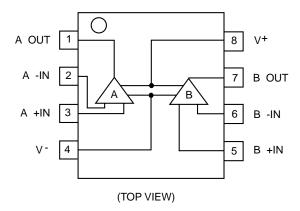

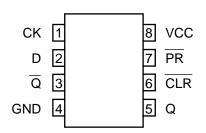

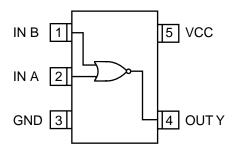

## ■ AK93C45AF-W (IC791) : CMOS EEPROM

#### 2.Pin Functions

| Symbol | Function           |  |  |  |

|--------|--------------------|--|--|--|

| CS     | Chip Select        |  |  |  |

| SK     | Serial Clock Input |  |  |  |

| DI     | Serial Data Input  |  |  |  |

| DO     | Serial Data Output |  |  |  |

| Vcc    | Power Supply       |  |  |  |

| GND    | Ground             |  |  |  |

| NC     | Non connection     |  |  |  |

#### 3.Block Diagram

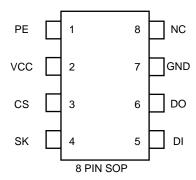

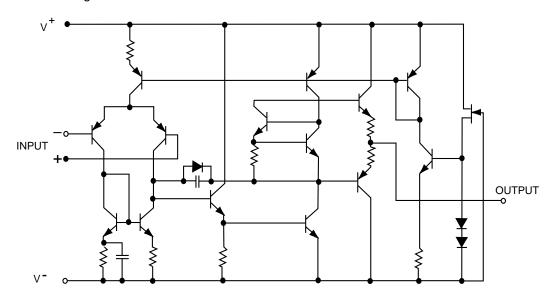

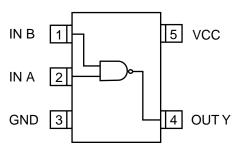

## ■ AK93C65AF-X (IC403) : EEPROM

#### 1.Terminal layout

### 2.Block diagram

#### 3.Pin function

| Pin no. | Symbol | Function                                        |  |  |  |  |  |

|---------|--------|-------------------------------------------------|--|--|--|--|--|

| 1       | PE     | Program enable (With built-in pull-up resistor) |  |  |  |  |  |

| 2       | VCC    | Power supply                                    |  |  |  |  |  |

| 3       | CS     | Chip selection                                  |  |  |  |  |  |

| 4       | SK     | Cereal clock input                              |  |  |  |  |  |

| 5       | DI     | Cereal data input                               |  |  |  |  |  |

| 6       | DO     | Cereal data output                              |  |  |  |  |  |

| 7       | GND    | Ground                                          |  |  |  |  |  |

| 8       | NC     | No connection                                   |  |  |  |  |  |

NOTE : The pull-up resistor of the PE pin is about 2.5M  $\Omega$  (VCC=5V)

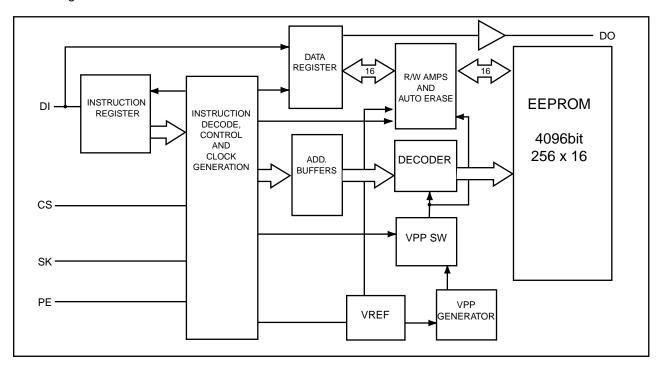

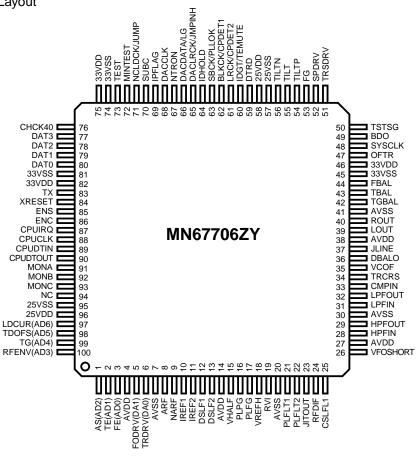

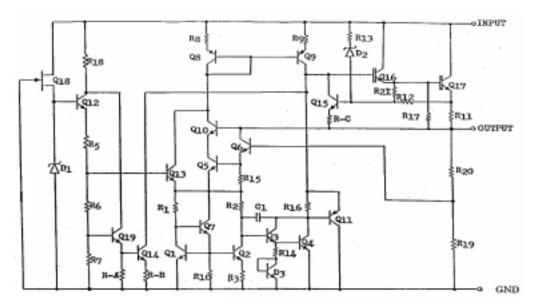

## ■ AN8702FH (IC101) : Front end processor

#### 1.Terminal Layout

#### 2.Pin Functions

| Pin No. | Symbol  | I/O | Function                                                          |

|---------|---------|-----|-------------------------------------------------------------------|

| 1       | PC1     |     |                                                                   |

| 2       | PC01    |     |                                                                   |

| 3       | PC2     |     |                                                                   |

| 4       | PC02    |     |                                                                   |

| 5       | TGBAL   | I   | Tangential phase balance control terminal                         |

| 6       | TBAL    | I   | Tracking balance control terminal                                 |

| 7       | FBAL    | I   | Focus balance control terminal                                    |

| 8       | POFLT   | 0   | Track detection threshold value level terminal                    |

| 9       | DTRD    | I   | Data slice part data read signal input terminal (For RAM)         |

| 10      | IDGT    | I   | Data slice part address part gate signal input terminal (For RAM) |

| 11      | STANDBY | I   | Standby mode control terminal                                     |

| 12      | SEN     | I   | SEN (Serial data input terminal)                                  |

| 13      | SCK     | I   | SCK (Serial data input terminal)                                  |

| 14      | STDI    | I   | STDI (Serial data input terminal)                                 |

| 15      | RSEL    |     |                                                                   |

| 16      | JLINE   |     |                                                                   |

| 17      | TEN     |     |                                                                   |

| 18      | TEOUT   | 0   | Tracking error signal output terminal                             |

| Pin No. | Symbol | I/O | Function                                                |

|---------|--------|-----|---------------------------------------------------------|

| 19      | ASN    |     |                                                         |

| 20      | ASOUT  |     |                                                         |

| 21      | FEN    | I   | Focus error output amplifier reversing input terminal   |

| 22      | FEOUT  | 0   | Focus error signal output terminal                      |

| 23      | VSS    | -   | Ground                                                  |

| 24      | TG     | 0   | Tangential phase error signal output terminal           |

| 25      | VDD    | -   | Apply 3V                                                |

| 26      | GND2   | -   | Ground                                                  |

| 27      | VREF2  | 0   | VREF2 voltage output terminal                           |

| 28      | VCC2   | -   | Apply 5V                                                |

| 29      | VHALF  | 0   | VHALF voltage output terminal                           |

| 30      | DFLTON |     |                                                         |

| 31      | DFLTOP |     |                                                         |

| 32      | DSFLT  |     |                                                         |

| 33      | GND3   | -   | Ground                                                  |

| 34      | RFDIFO |     |                                                         |

| 35      | RFOUT  |     |                                                         |

| 36      | VCC3   | -   | Apply 5V                                                |

| 37      | RFC    |     |                                                         |

| 38      | DCRF   | 0   | All addition amplifier capacitor terminal               |

| 39      | OFTR   | 0   | OFTR output terminal                                    |

| 40      | BDO    |     |                                                         |

| 41      | RFENV  | 0   | RF envelope output terminal                             |

| 42      | воттом | 0   | Bottom envelope detection filter terminal               |

| 43      | PEAK   | 0   | Peak envelope detection filter terminal                 |

| 44      | AGCG   | 0   | AGC amplifier gain control terminal                     |

| 45      | AGCO   |     |                                                         |

| 46      | TESTSG | I   | TEST signal input terminal                              |

| 47      | RFINP  | I   | RF signal positive input terminal                       |

| 48      | RFINN  | I   | RF signal negative input terminal                       |

| 49      | VIN5   | I   | Focus input of external division into two terminal      |

| 50      | VIN6   | 1   | Focus input of external division into two terminal      |

| 51      | VIN7   | I   |                                                         |

| 52      | VIN8   | I   | I                                                       |

| 53      | VIN9   | I   |                                                         |

| 54      | VIN10  | I   |                                                         |

| 55      | VCC1   | -   | Apply 5V                                                |

| 56      | VREF1  | 0   | VREF1 voltage output terminal                           |

| 57      | VIN1   | I   | External division into four (DVD/CD) RF input terminal1 |

| 58      | VIN2   | I   | External division into four (DVD/CD) RF input terminal2 |

| 59      | VIN3   | I   | External division into four (DVD/CD) RF input terminal3 |

| 60      | VIN4   | I   | External division into four (DVD/CD) RF input terminal4 |

| 61      | GND1   | -   | Ground                                                  |

| 62      | VIN11  | I   |                                                         |

| 63      | VIN12  | I   |                                                         |

| 64      | HDTYPE |     |                                                         |

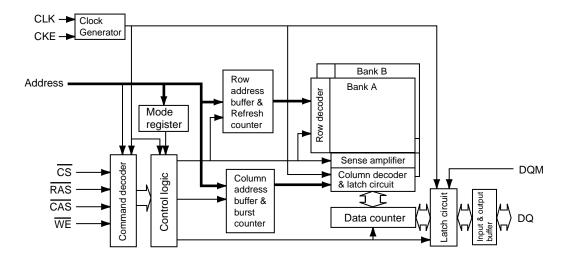

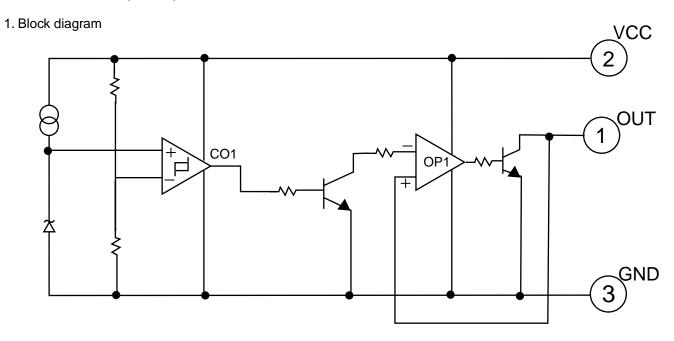

## ■ HY57V161610DTC8 or KM416S1120DT-G8 (IC504,IC505): 16MB SDRAM

### 1.Block diagram

| Pin No. | Symbol | Description           | Pin No. | Symbol  | Description          |

|---------|--------|-----------------------|---------|---------|----------------------|

| 1       | VCC    | Power supply          | 26      | VSS     | Connect to GND       |

| 2,3     | DQ0,1  | Data input/output     | 27~32   | A4~9    | Address inputs       |

| 4       | VSS    | Connect to GND        | 33      | NC      | Non connect          |

| 5,6     | DQ2,3  | Data input/output     | 34      | CKE     | Clock enable         |

| 7       | VDD    | Power supply          | 35      | CLK     | System clock input   |

| 8,9     | DQ4,5  | Data input/output     | 36      | UDQM    | Upper DQ mask enable |

| 10      | VSS    | Connect to GND        | 37      | NC      | Non connect          |

| 11,12   | DQ6,7  | Data input/output     | 38      | VCC     | Power supply         |

| 13      | VCC    | Power supply          | 39,40   | DQ8,9   | Data input/output    |

| 14      | LDQM   | Lower DQ mask enable  | 41      | VSS     | Connect to GND       |

| 15      | WE     | Write enable          | 42,43   | DQ10,11 | Data input/output    |

| 16      | CAS    | Column address strobe | 44      | VDD     | Power supply         |

| 17      | RAS    | Row address strobe    | 45,46   | DQ12,13 | Data input/output    |

| 18      | CS     | Chip enable           | 47      | VSS     | Connect to GND       |

| 19,20   | A11,10 | Address inputs        | 48,49   | DQ14,15 | Data input/output    |

| 21~24   | A0~3   | Address inputs        | 50      | VSS     | Connect to GND       |

| 25      | VCC    | Power supply          |         |         |                      |

| No. | Symbol        | I/O | Function                                    | No. | Symbol  | I/O | Function                                         |

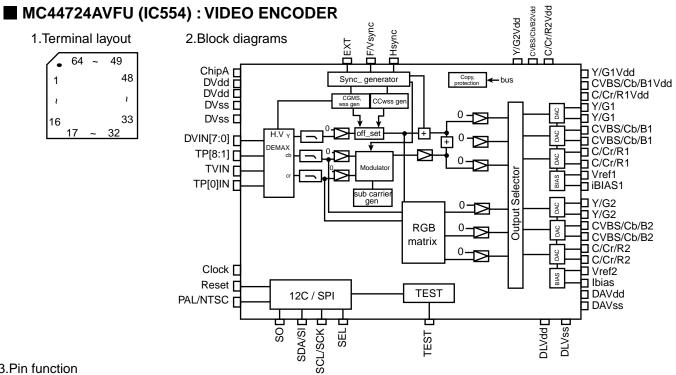

|-----|---------------|-----|---------------------------------------------|-----|---------|-----|--------------------------------------------------|

| 1   | CVBS/Cb/B1    | 0   | Analog composite drive signal (+)           | 33  | SO      | -   | Non connect                                      |

| 2   | CVBS/Cb/B1    | 0   | Analog composite drive signal (-)           | 34  | SDA/SI  | ı   | SPI Mode : Serial data input                     |

| 3   | CVBS/Cb/B1Vdd | -   | Power supply for CVBS/Cb/B DAC1             | 35  | SCL/SCK | ı   | Serial clock input                               |

| 4   | Y/G1          | 0   | Analog brightness signal/G drive signal (+) | 36  | SEL     | Ι   | Power supply for serial data,chip select,digital |

| 5   | Y/G1          | 0   | Analog brightness signal/G drive signal (-) | 37  | DVdd    |     | Power supply for digital circuit                 |

| 6   | Y/G1/Vdd      | -   | Power supply for Y/G DAC                    | 38  | DVss    |     | Digital ground                                   |

| 7   | C/Cr/R1       | 0   | Analog chroma signal (+)                    | 39  | DVIN7   | I/O | Y data input / test data I/O                     |

| 8   | C/Cr/R1       | 0   | Analog chroma signal (-)                    | 40  | DVIN6   | I/O | Y data input / test data I/O                     |

| 9   | C/Cr/R1Vdd    | -   | Power supply for C/Cr/RDAC                  | 41  | DVIN5   | I/O | Y data input / test data I/O                     |

| 10  | DAVss         | -   | Connect to ground for DAC                   | 42  | DVIN4   | I/O | Y data input / test data I/O                     |

| 11  | TBIAS1        | 0   | Standard BIAS for DAC1                      | 43  | DVIN3   | I/O | Y data input / test data I/O                     |

| 12  | Vref1         | -   | Standard voltage for DAC1                   | 44  | DVIN2   | I/O | Y data input / test data I/O                     |

| 13  | DAVdd         | -   | Power supply for DAC                        | 45  | DVIN1   | I/O | Y data input / test data I/O                     |

| 14  | Vref2         | -   | Standard voltage for DAC2                   | 46  | DVIN0   | I/O | Y data input / test data I/O                     |

| 15  | TBIAS2        | 0   | Standard BIAS for DAC2                      | 47  | TVIN    | Ι   | VIDEO mute on Reset(0:nomal, 1:mute)             |

| 16  | NC            | -   | Non connect                                 | 48  | EXT     | I/O | Frame output / VBI information input             |

| 17  | CVBS/Cb/B2    | 0   | Analog composite drive signal (+)           | 49  | F/Vsyac | I/O | Frame / Vertical, synchronous I/O                |

| 18  | CVBS/Cb/B2    | 0   | Analog composite drive signal (-)           | 50  | Chsyac  | I/O | The horizontal, synchronous I/O                  |

| 19  | CVBS/Cb/B2Vdd | -   | Power supply for CVBS/Cb/B DAC2             | 51  | DATST   | ı   | Data input                                       |

| 20  | Y/G2          | 0   | Analog brightness signal/G drive signal (+) | 52  | TP-8    | I/O | Multiplex data input                             |

| 21  | Y/G2          | 0   | Analog brightness signal/G drive signal (-) | 53  | TP7     | I/O | Multiplex data input                             |

| 22  | Y/GVdd        | -   | Power supply for Y/G DAC                    | 54  | TP6     | I/O | Multiplex data input                             |

| 23  | C/Cr/R2       | 0   | Analog chroma signal (+)                    | 55  | TP5     | I/O | Multiplex data input                             |

| 24  | C/Cr/R2       | 0   | Analog chroma signal (-)                    | 56  | DVss    | -   | Ground for digital circuit                       |

| 25  | C/Cr/R2Vdd    | -   | Power supply for C/Cr/RDAC2                 | 57  | DVdd    | -   | Power supply for digital circuit                 |

| 26  | ChipA         | -   | Chip address selection                      | 58  | TP4     | I/O | Data input / Test data I/O                       |

| 27  | TEST          | I   | Connect to test pin                         | 59  | TP3     | I/O | Data input / Test data I/O                       |

| 28  | DVdd          | -   | Digital ground                              | 60  | TP2     | I/O | Data input / Test data I/O                       |

| 29  | CLOCK         | ı   | Clock signal input (27MHz)                  | 61  | TP1     | I/O | Data input / Test data I/O                       |

| 30  | DVss          | -   | Power supply for digital circuit            | 62  | TP0     | I/O | Data input / Test data I/O                       |

| 31  | Reset         | I   | Reset signal input L:ON                     | 63  | DLVdd   | -   | Power supply for D/A converter                   |

| 32  | PAL/NTSC      | I   | Selection NTSC/PAL NTSC:L PAL:H             | 64  | DLVss   | -   | Ground for D/A converter                         |

## ■ MN101C12GHA (IC701) : System micom

### 1.Terminal layout

| Pin No. | Symbol    | I/O | Function                                                               |  |  |  |  |  |  |

|---------|-----------|-----|------------------------------------------------------------------------|--|--|--|--|--|--|

| 1       | GND       | - 1 |                                                                        |  |  |  |  |  |  |

| 2       | CS0       | I   | Setup bit 0 (Effective with U/E versions) software pull-up? available. |  |  |  |  |  |  |

| 3       | CS1       | ı   | Setup bit 1 (Effective with U/E versions) software pull-up? available. |  |  |  |  |  |  |

| 4       | CS2       | I   | Setup bit 2 (Effective with U/E versions) software pull-up? available. |  |  |  |  |  |  |

| 5       | NTSEL     | ı   | NTSC/PAL Input select switch                                           |  |  |  |  |  |  |

| 6       | POWERSW   | I   | Power key Input                                                        |  |  |  |  |  |  |

| 7       | SAFETEY   | I   |                                                                        |  |  |  |  |  |  |

| 8       |           |     |                                                                        |  |  |  |  |  |  |

| 9       |           | I   |                                                                        |  |  |  |  |  |  |

| 10      | VREF+     | -   |                                                                        |  |  |  |  |  |  |

| 11      | VDD       | -   |                                                                        |  |  |  |  |  |  |

| 12      | OSC2      | 0   | 10MHz                                                                  |  |  |  |  |  |  |

| 13      | OSC1      | ı   |                                                                        |  |  |  |  |  |  |

| 14      | VSS       | -   |                                                                        |  |  |  |  |  |  |

| 15      | -         | ı   | Not used. Connect to GND                                               |  |  |  |  |  |  |

| 16      | -         | 0   | Not used.                                                              |  |  |  |  |  |  |

| 17      | MMOD      | ı   | Connect to GND                                                         |  |  |  |  |  |  |

| 18      | OSDCS3    | 0   | V. ENCODER Chip select                                                 |  |  |  |  |  |  |

| 19      | RSTE      | 0   | V. ENCODER Reset                                                       |  |  |  |  |  |  |

| 20      | OSDDO     | 0   | V.ENCODER Communications DATA                                          |  |  |  |  |  |  |

| 21      | S2UDT     | 0   | Communications DATA OUT between the Unit and the Microprocessor        |  |  |  |  |  |  |

| 22      | U2SDT     | ı   | Communications DATA IN between the Unit and the Microprocessor         |  |  |  |  |  |  |

| 23      | SCLK      | 0   | Communications CLK between the Unit and the Microprocessor             |  |  |  |  |  |  |

| 24      | BUSY      | 0   | Communications BUSY between the Unit and the Microprocessor            |  |  |  |  |  |  |

| 25      | CPURST    | 0   | Unit microprocessor Reset                                              |  |  |  |  |  |  |

| 26      | REQ       | ı   | Communications REQ between the Unit and the Microprocessor             |  |  |  |  |  |  |

| 27      | REMO      |     | Remote control interruption                                            |  |  |  |  |  |  |

| 28      | CS3       |     | Setup password change judging bit (H change, L Normally)               |  |  |  |  |  |  |

| 29      |           |     |                                                                        |  |  |  |  |  |  |

| 30      | TEST      | !!  | H: Checker mode, L: Normal mode                                        |  |  |  |  |  |  |

| 31      | TEST      |     |                                                                        |  |  |  |  |  |  |

| 32      |           | !!  | 5                                                                      |  |  |  |  |  |  |

| 33      | RESET     | 1   | Reset Input                                                            |  |  |  |  |  |  |

| 34      | MT0       | 0   | Tray motor control 0                                                   |  |  |  |  |  |  |

| 35      | MT1       | 0   | Tray motor control 1                                                   |  |  |  |  |  |  |

| 36      | 00001     | 0   | V 51000550                                                             |  |  |  |  |  |  |

| 37      | OSDCK     | 0   | V. ENCODER Communications CK                                           |  |  |  |  |  |  |

| 38      | NT        | 0   | NTSC/PAL Switching (V. ENCODER)                                        |  |  |  |  |  |  |

| 39      | FS2       | 0   | 48kHz/96kHz Switching                                                  |  |  |  |  |  |  |

| 40      | OPEN      | !   | Tray OPEN Switch detection Software pull-up??? available               |  |  |  |  |  |  |

| 41      | CLOSE     | I   | Tray CLOSE Switch detection Software pull-up??? available              |  |  |  |  |  |  |

| 42      |           | 0   |                                                                        |  |  |  |  |  |  |

| 43      |           | 0   |                                                                        |  |  |  |  |  |  |

| 44      | EL DATA O | 0   | El Driver Consequeir etiere DATA C                                     |  |  |  |  |  |  |

| 45      | FLDATAO   | 0   | FL Driver Communications DATA 0                                        |  |  |  |  |  |  |

MN101C12GHA (2/2)

|          |            |     | WINTOTOTZGTIA (ZZ)                        |

|----------|------------|-----|-------------------------------------------|

| Pin No.  | Symbol     | I/O | Function                                  |

| 46       | FLDATAI    | 1   | FL Driver Communications DATA 1           |

| 47       | FLCK       | 0   | FL Driver Communications CLOCK            |

| 48       | FLCS       | 0   | FL Driver Communications CS               |

| 49       | FLRST      | 0   |                                           |

| 50       | EEDO       | 0   | EEPROM Communications DATA 0              |

| 51       | EEDI       | I   | EEPROM Communications DATA 1              |

| 52       | EECK       | 0   | EEPROM Communications CLOCK               |

| 53       | EECS       | 0   | EEPROM Communications CS                  |

| 54       | VS1        | 0   | S1 Control                                |

| 55       | VS3        | 0   | S3 Control (STBY:H, P.ON:L)               |

| 56       |            | 0   |                                           |

| 57       |            | 0   |                                           |

| 58       |            | 0   |                                           |

| 59       |            | 0   |                                           |

| 60       |            | 0   |                                           |

| 61       |            | 0   |                                           |

| 62       |            | 0   |                                           |

| 63       | KARAOKE    | 0   | KARAOKE Gain Control (For KARAOKE, set H) |

| 64       | POWERON    | 0   | POWER ON OUTPUT                           |

| 65       |            | 0   |                                           |

| 66       |            | 0   |                                           |

| 67       |            | 0   |                                           |

| 68       |            | 0   |                                           |

| 69       |            | 0   |                                           |

| 70       |            | 0   |                                           |

| 71       |            | 0   |                                           |

| 72       |            | 0   |                                           |

| 73       |            | 0   |                                           |

| 74       |            | 0   |                                           |

| 75       |            | 0   |                                           |

| 76<br>77 | A) (C4     | 0   | AV COMPULINK INPUT                        |

|          | AVC1       | 1   |                                           |

| 78       | AVCO       | 0   | AV COMPULINK OUTPUT                       |

| 79       | STANBYIND  | 0   | STANDBY LED OUTPUT                        |

| 80<br>81 | STAINDTIND | 0   | STANDET LED OUTPUT                        |

| 82       |            | 0   |                                           |

| 83       |            | 0   |                                           |

| 84       |            | 0   |                                           |

| 85       |            | 0   |                                           |

| 86       |            | 0   |                                           |

| 87       | MA         | 0   | DAC Control MA                            |

| 88       | MB         | 0   | DAC CONTROL MA  DAC Control MB            |

| 89       | M1M3       | Ö   | DAC Control M1M3                          |

| 90       | MD         | 0   | DAC Control MD                            |

| 91       | MC         | 0   | DAC COntrol MC                            |

| 92       | 1410       | 0   | DAG GOALLOLING                            |

| 93       |            | 0   |                                           |

| 94       |            | ő   |                                           |

| 95       | DAVSS      | -   |                                           |

| 96       | 200        | 0   |                                           |

| 97       |            | Ö   |                                           |

| 98       |            | ŏ   |                                           |

| 99       | MUTE       | Ö   | Front Mute OUTPUT                         |

| 100      | DAVDD      | -   |                                           |

|          | • -        |     |                                           |

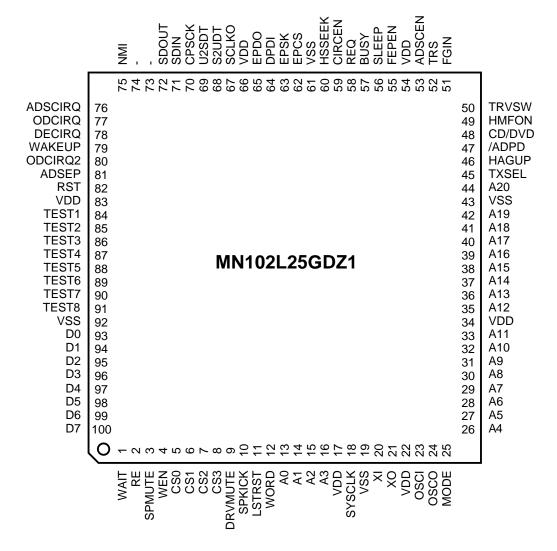

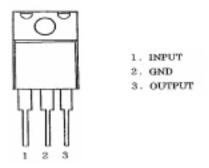

#### ■ MN102L25GDZ1 (IC401): UNIT CPU

#### 1.Terminal layout

| Pin No. | Symbol  | I/O | Function                     | Pin No. | Symbol       | I/O      | Function                                        |

|---------|---------|-----|------------------------------|---------|--------------|----------|-------------------------------------------------|

| 1       | WAIT    | 1   | Micon wait signal input      | 51      | FGIN         | 1        | Photo input                                     |

| 2       | RE      | Ö   | Read enable                  | 52      | TRS          | t i      |                                                 |

| 3       | SPMUTE  | Ō   |                              | 53      | ADSCEN       | 0        | Serial enable signal for ADSC                   |

| 4       | WEN     | 0   | Write enable                 | 54      | VDD          | -        | Power supply                                    |

| 5       | CS0     | Ō   | Non connect                  | 55      | FEPEN        | 0        | Serial enable signal for FEP                    |

| 6       | CS1     | Ō   | Chip select for ODC          | 56      | SLEEP        | ō        | Standby signal for FEP                          |

| 7       | CS2     | Ō   | Chip select for ZIVA         | 57      | BUSY         | Ť        | Communication busy                              |

| 8       | CS3     | Ō   | Chip select for outer ROM    | 58      | REQ          | Ö        | Communication Request                           |

| 9       | DRVMUTE | Ō   | Driver mute                  | 59      | CIRCEN       | ō        | CIRC command select                             |

| 10      | SPKICK  | Ō   | Spin kick (Non connect)      | 60      | HSSEEK       | ō        | Seek select                                     |

| 11      | LSIRST  | Ō   | LSI reset                    | 61      | VSS          | -        | Ground                                          |

| 12      | WORD    | Ö   | Bus selection input          | 62      | EPCS         | 0        | EEPROM chip select                              |

| 13      | A0      | Ö   | Address bus 0 for CPU        | 63      | EPSK         | ō        | EEPROM clock                                    |

| 14      | A1      | Ö   | Address bus 1 for CPU        | 64      | DPDI         | Ť        | EEPROM data input                               |

| 15      | A2      | Ö   | Address bus 2 for CPU        | 65      | EPDO         | Ö        | EEPROM data output                              |

| 16      | A3      | Ö   | Address bus 3 for CPU        | 66      | VDD          | -        | Power supply                                    |

| 17      | VDD     | -   | Power supply                 | 67      | SCLKO        |          | Communication clock                             |

| 18      | SYSCLK  | 0   | System clock signal output   | 68      | S2UDT        | H        | Communication input data                        |

| 19      | VSS     | -   | Ground                       | 69      | U2SDT        | ö        | Communication output data                       |

| 20      | XI      | -   | Not use (Connect to vss)     | 70      | CPSCK        | ŏ        | Clock for ADSC serial                           |

| 21      | XO      | -   | Non connect                  | 71      | SDIN         | H        | ADSC serial data input                          |

| 22      | VDD     | -   | Power supply                 | 72      | SDOUT        | 6        | ADSC serial data input  ADSC serial data output |

| 23      | OSCI    | 1   | Clock signal input(13.5MHz)  | 73      | <u> </u>     | -        | Not use                                         |

| 24      | OSCO    | 0   | Clock signal output(13.5MHz) | 74      | -            | -        | Not use                                         |

| 25      | MODE    | Ť   | CPU Mode selection input     | 75      | NMI          | -        | Not use                                         |

| 26      | A4      | 0   | Address bus 4 for CPU        | 76      | ADSCIRQ      | -        | Interrupt input of ADSC                         |

| 27      |         | 0   | Address bus 5 for CPU        | 77      | ODCIRQ       | +        | Interrupt input of ADSC                         |

| 28      | A5      | 0   | Address bus 6 for CPU        |         |              | 1        | Interrupt input of ZIVA                         |

| 29      | A6      | 0   | Address bus 7 for CPU        | 78      | DECIRQ       | 6        | Not use                                         |

| 30      | A7      | 0   | Address bus 8 for CPU        | 79      | WAKEUP       | 1        | Not use                                         |

| 31      | A8      | 0   | Address bus 9 for CPU        | 80      | ODCIRQ2      | <u> </u> | Address data selection input                    |

| 32      | A9      | 0   | Address bus 10 for CPU       | 81      | ADSEP        | <u> </u> | Reset input                                     |

| 33      | A10     | 0   | Address bus 11 for CPU       | 82      | RST          | -        | Power supply                                    |

| 34      | A11     |     | Power supply                 | 83      | VDD<br>TECT4 | -        | Test signal 1 input                             |

| 35      | VDD     | -   | Address bus 12 for CPU       | 84      | TEST1        | -        | ·                                               |

| 36      | A12     | 0   | Address bus 13 for CPU       | 85      | TEST2        |          | Test signal 2 input                             |

| 37      | A13     | 0   |                              | 86      | TEST3        |          | Test signal 4 input                             |

|         | A14     | 0   | Address bus 14 for CPU       | 87      | TEST4        | -        | Test signal 4 input                             |

| 38      | A15     | 0   | Address bus 15 for CPU       | 88      | TEST5        |          | Test signal 5 input                             |

| 39      | A16     | 0   | Address bus 16 for CPU       | 89      | TEST6        | -        | Test signal 6 input                             |

| 40      | A17     | 0   | Address bus 17 for CPU       | 90      | TEST7        | -        | Test signal 7 input                             |

| 41      | A18     | 0   | Address bus 18 for CPU       | 91      | TEST8        |          | Test signal 8 input                             |

| 42      | A19     | 0   | Address bus 19 for CPU       | 92      | VSS          | -        | Ground                                          |

| 43      | VSS     | -   | Ground                       | 93      | D0           | 1/0      | Data bus 0 of CPU                               |

| 44      | A20     | 0   | Address bus 20 for CPU       | 94      | D1           | 1/0      | Data bus 1 of CPU                               |

| 45      | TXSEL   | 0   | TX Select                    | 95      | D2           | 1/0      | Data bus 2 of CPU                               |

| 46      | HAGUP   | 0   |                              | 96      | D3           | 1/0      | Data bus 3 of CPU                               |

| 47      | /ADPD   |     |                              | 97      | D4           | 1/0      | Data bus 4 of CPU                               |

| 48      | CD/DVD  | 0   |                              | 98      | D5           | 1/0      | Data bus 5 of CPU                               |

| 49      | HMFON   |     | <b>D</b> ( ) ( ) ( )         | 99      | D6           | 1/0      | Data bus 6 of CPU                               |

| 50      | TRVSW   | I   | Detection switch of traverse | 100     | D7           | I/O      | Data bus 7 of CPU                               |

|         |         |     | inside                       |         |              |          |                                                 |

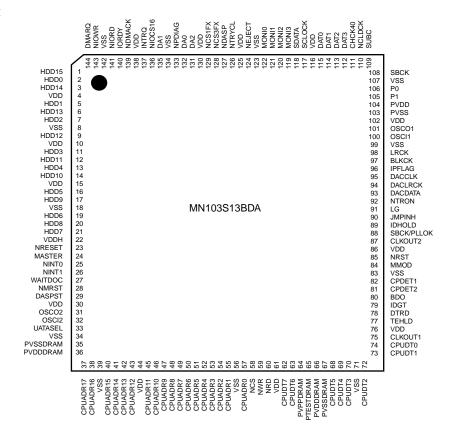

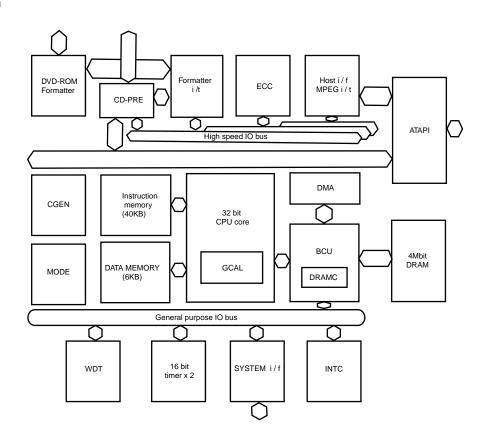

### MN103S13BDA (IC301): Optical disc controller

#### 1.Terminal layout

#### 2.Block diagram

| Pin NO.  | Symbol               | I/O                                              | Function                                      |

|----------|----------------------|--------------------------------------------------|-----------------------------------------------|

| 1        | HDD15                | I/O                                              | ATAPI data                                    |

| 2        | HDD0                 | I/O                                              | ATAPI data                                    |

| 3        | HDD14                | I/O                                              | ATAPI data                                    |

| 4        | VDD                  | <b> </b>                                         | Apply 3V                                      |

| 5        | HDD1                 | I/O                                              | ATAPI data                                    |

| 6        | HDD13                | I/O                                              | ATAPI data                                    |

| 7        | HDD2                 | I/O                                              | ATAPI data                                    |

| 8        | VSS                  | -                                                | GND                                           |

| 9        | HDD12                | I/O                                              | ATAPI data                                    |

| 10       | VDD                  | -                                                | Apply 2.7V                                    |

| 11       | HDD3                 | I/O                                              | ATAPI data                                    |

| 12       | HDD11                | I/O                                              | ATAPI data                                    |

| 13       | HDD4                 | I/O                                              | ATAPI data                                    |

| 14       | HDD10                | I/O                                              | ATAPI data                                    |

| 15       | VDD                  | -                                                | Apply 3V                                      |

| 16       | HDD5                 | I/O                                              | ATAPI data                                    |

| 17       | HDD9                 | I/O                                              | ATAPI data                                    |

| 18       | VSS                  | -                                                | GND                                           |

| 19       | HDD6                 | I/O                                              | ATAPI data                                    |

| 20       | HDD8                 | I/O                                              | ATAPI data                                    |

| 21       | HDD7                 | I/O                                              | ATAPI data                                    |

| 22       | VDDH                 |                                                  |                                               |

| 23       | NRESET               | I                                                | ATAPI reset                                   |

| 24       | MASTER               | I/O                                              | ATAPI master / slave selection                |

| 25       | NINT0                | 0                                                | System control interruption 0                 |

| 26       | NINT1                | 0                                                | System control interruption 1                 |

| 27       | WAITDOC              | 0                                                | System control wait control                   |

| 28       | NMRST                | 0                                                | System control reset (Connect to TP302)       |

| 29       | DASPST               | I                                                | DASP signal initializing (VSS connected)      |

| 30       | VDD                  | -                                                | Apply 3V                                      |

| 31       | OSCO2                | 0                                                | OPEN (Connect to TP140)                       |

| 32       | OSCI2                |                                                  | OPEN (Connect to TP303)                       |

| 33       | UATASEL              |                                                  | VSS connected                                 |

| 34       | VSS                  | -                                                | GND                                           |

| 35       | PVSSDRAM             |                                                  | VSS connected                                 |

| 36       | PVDDDRAM             | + -                                              | VDD (2.7V) connected                          |

| 37       | CPUADR17             |                                                  | System control address                        |

| 38       | CPUADR16             |                                                  | System control address GND                    |

| 39<br>40 | VSS<br>CPUADR15      | -                                                | System control address                        |

| 40       | CPUADR15             | +                                                | System control address System control address |

| 41       | CPUADR14<br>CPUADR13 | <br>                                             | System control address System control address |

| 42       | CPUADR13             | $+ \div +$                                       | System control address System control address |

| 43       | VDD                  | <del>                                     </del> | Apply 2.7V                                    |

| 45       | CPUADR11             | <del>  -</del>                                   | System control address                        |

| 45       | OF UNDR 11           |                                                  | Gystern control address                       |

| Pin NO. | Symbol     | I/O | Function                                              |

|---------|------------|-----|-------------------------------------------------------|

| 46      | CPUADR10   | ı   | System control address                                |

| 47      | CPUADR9    | i   | System control address                                |

| 48      | CPUADR8    | I   | System control address                                |

| 49      | CPUADR7    | I   | System control address                                |

| 50      | CPUADR6    | Ι   | System control address                                |

| 51      | CPUADR5    | I   | System control address                                |

| 52      | CPUADR4    | I   | System control address                                |

| 53      | CPUADR3    | 1   | System control address                                |

| 54      | CPUADR2    | I   | System control address                                |

| 55      | CPUADR1    | I   | System control address                                |

| 56      | VSS        | -   | GND                                                   |

| 57      | CPUADR0    | I   | System control address                                |

| 58      | NCS        | I   | System control chip selec                             |

| 59      | NWR        | - 1 | System control write                                  |

| 60      | NRD        | I   | System control read                                   |

| 61      | VDD        | -   | Apply 3V                                              |

| 62      | CPUDT7     | I/O | System control data                                   |

| 63      | CPUDT6     | I/O | System control data                                   |

| 64      | PVPPDRAM   | 0   | VSS connected                                         |

| 65      | PTESTDRAM  | I   | VSS connected                                         |

| 66      | PVDDDRAM   |     | VDD (2.7V) connected                                  |

| 67      | PVSSDRAM   |     | VSS connected                                         |

| 68      | CPUDT5     | I/O | System control data                                   |

| 69      | CPUDT4     | I/O | System control data                                   |

| 70      | CPUDT3     | I/O | System control data                                   |

| 71      | VSS        | -   | GND                                                   |

| 72      | CPUDT2     | I/O | System control data                                   |

| 73      | CPUDT1     | I/O | System control data                                   |

| 74      | CPUDT0     | I/O | System control data                                   |

| 75      | CLKOUT1    | 0   | 16.9/11.2/8.45MHz clock                               |

| 76      | VDD        | -   | Apply 3V                                              |

| 77      | TEHLD      | 0   | Mirror gate (Connect to TP141)                        |

| 78      | DTRD       | 0   | Data part frequency control switch (Connect to TP304) |

| 79      | IDGT       | 0   | Part CAPA switch (Connect to TP305)                   |

| 80      | BDO        | I   | RF dropout / BCA data of making to binary             |

| 81      | CPDET2     | 1   | Outer side CAPA detection                             |

| 82      | CPDET1     | I   | Side of surroundings on inside                        |

| 83      | VSS        | -   | GND                                                   |

| 84      | MMOD       | I   | VSS connected                                         |

| 85      | NRST       | I   | System reset                                          |

| 86      | VDD        | -   | Apply 3V                                              |

| 87      | CLKOUT2    | 0   | 16.9MHz clock                                         |

| 88      | SBCK/PLLOK | 0   | Frame mark detection                                  |

| 89      | IDOHOLD    | 0   | ID gate for tracking holding (Connect to TP307)       |

| 90      | JMPINH     | 0   | Jump prohibition                                      |

| Pin NO. | Symbol  | I/O | Function                                                   |

|---------|---------|-----|------------------------------------------------------------|

| 91      | LG      | 0   | Land / group switch                                        |

| 92      | NTRON   | ı   | Tracking ON                                                |

| 93      | DACDATA | 0   | Sereal output (Connect to TP148)                           |

| 94      | DACLRCK | 0   | L and R identification output (Connect to TP149)           |

| 95      | DACCLK  | ı   | Clock for serial output                                    |

| 96      | IPFLAG  | I   | Interpolation flag input                                   |

| 97      | BLKCK   | ı   | Sub-code,Block clock input (VSS connected)                 |

| 98      | LRCK    | ı   | L and R identification signal output (VSS connected)       |

| 99      | VSS     | -   | GND                                                        |

| 100     | OSCI1   | ı   | 16.9MHz oscillation                                        |

| 101     | OSCO1   | 0   | 16.9MHz oscillation                                        |

| 102     | VDD     | -   | Apply 3V                                                   |

| 103     | PVSS    | -   | GND                                                        |

| 104     | PVDD    | -   | Apply 3V                                                   |

| 105     | P1      | I/O | Terminal MASTER polarity switch input (VDD 3V connected)   |

| 106     | P0      | I/O | CIRC-RAM OVER/UNDER                                        |

|         |         |     | Interruption signal input (VDD 3V connected)               |

| 107     | VSS     | -   | GND                                                        |

| 108     | SBCK    | 0   | Sub-code, Clock output for serial input (Connect to TP306) |

| 109     | SUBC    | ı   | Sub-code, Serial input                                     |

| 110     | NCLDCK  | ı   | Sub-code, Frame clock input                                |

| 111     | CHCK40  | ı   | Read clock to DAT3~0                                       |

|         |         |     | (Output of dividing frequency four from ADSC)              |

| 112     | DAT3    | ı   | Read data from DISC                                        |

| 113     | DAT2    | 1   | (Parallel output from ADSC)                                |

| 114     | DAT1    | ı   |                                                            |

| 115     | DAT0    |     |                                                            |

| 116     | VDD     | -   | Apply 3V                                                   |

| 117     | SCLOCK  | I/O | Debugging serial clock (Not use)                           |

|         |         |     | $(270\Omega\mathrm{pull}\mathrm{up})$                      |

| 118     | SDATA   | I/O | Debugging serial data (Not use)                            |

|         |         |     | (270Ω pull up)                                             |

| 119     | MONI3   | 0   | Internal goods title monitor (Connect to TP150-TP153)      |

| 120     | MONI2   | 0   |                                                            |

| 121     | MONI1   | 0   |                                                            |

| 122     | MONI0   | 0   |                                                            |

| 123     | VSS     | -   | GND                                                        |

| 124     | NEJECT  | ı   | Eject detection                                            |

| 125     | VDD     | -   | Apply 2.7V                                                 |

| 126     | NTRYCL  | I   | Tray close detection (Not use)                             |

| 127     | NDASP   | I/O | ATAPI Drive active/                                        |

|         |         |     | Slave connection I/O                                       |

| 128     | NCS3FX  | I   | ATAPI host chip selec (Not use)                            |

| 129     | NCS1FX  | I   | ATAPI host chip selec (Not use)                            |

| 130     | VDD     | -   | Apply 3V                                                   |

| 131     | DA2     | I/O | ATAPI host address                                         |

| 132     | DA0     | I/O | ATAPI host address (Not use)                               |

| Pin NO. | Symbol  | I/O | Function                                            |

|---------|---------|-----|-----------------------------------------------------|

| 133     | NPDIAG  | I/O | ATAPI slave master diagnosis input                  |

| 134     | VSS     | -   | GND                                                 |

| 135     | DA1     | I/O | ATAPI host address (Not use)                        |

| 136     | NIOCS16 | 0   | ATAPI output of selection of width of host data bus |

| 137     | INTRQ   | 0   | ATAPI host interruption output                      |

| 138     | VDD     | -   | Apply 3V                                            |

| 139     | NDMACK  | -   | ATAPI host DMA response (Not use)                   |

| 140     | IORDY   | 0   | ATAPI host ready output (Connect to TP157)          |

| 141     | NIORD   | I   | ATAPI host read (Not use)                           |

| 142     | VSS     | -   | GND                                                 |

| 143     | NIOWR   | I/O | ATAPI host writes                                   |

| 144     | DMARQ   | 0   | ATAPI host DMA request (Connect to TP159)           |

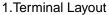

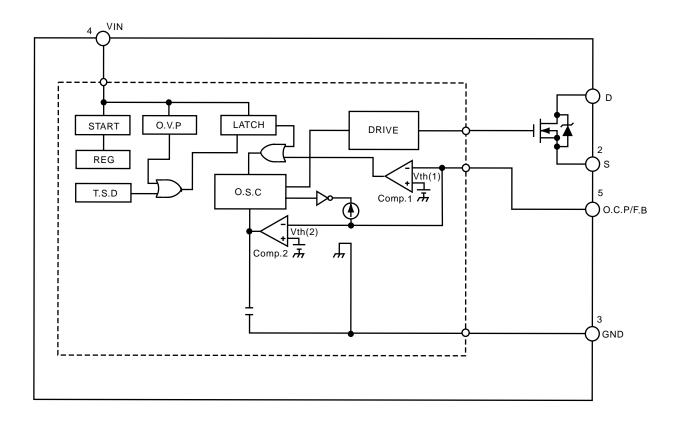

#### ■ MN67706ZY (IC201): ADSC

#### 2.Pin Functions

| Pin No. | Symbol     | I/O | Function                                               |

|---------|------------|-----|--------------------------------------------------------|

| 1       | AS(AD2)    | I   | AS : Full adder signal(FEP)                            |

| 2       | TE(AD1)    | I   | Phase difference/3 beam tracking error(FEP)            |

| 3       | FE(AD0)    | I   | Focus error(FEP)                                       |

| 4       | AVDD       | -   | Apply 3.3V(For analog circuit)                         |

| 5       | FODRV(DA1) | 0   | Focus drive(DRVIC)                                     |

| 6       | TRDRV(DA0) | 0   | Tracking drive(DRVIC)                                  |

| 7       | AVSS       | -   | Ground(For analog circuit)                             |

| 8       | ARF        |     | Equivalence RF+(FEP)                                   |

| 9       | NARF       |     | Equivalence RF-(FEP)                                   |

| 10      | IREF1      | I   | Reference current1(For DBAL)                           |

| 11      | IREF2      | I   | Reference current2(For DBAL)                           |

| 12      | DSLF1      | I/O | Connect to capacitor1 for DSL                          |

| 13      | DSLF2      | I/O | Connect to capacitor2 for DSL                          |